2025-02-20

-ALINX NVME SPCle IP -

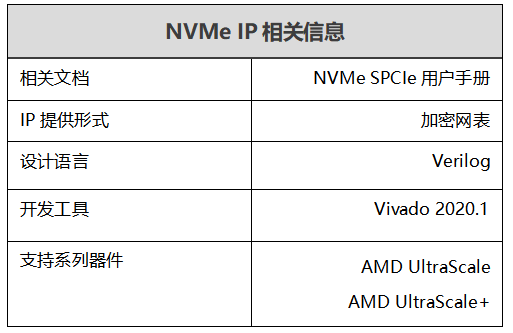

在嵌入式設(shè)備、邊緣計(jì)算、工業(yè)控制等領(lǐng)域快速崛起的同時(shí),開發(fā)人員越來越多地面對(duì)一個(gè)問題: 硬件資源有限,但對(duì)高速存儲(chǔ)的需求卻越來越高。這些平臺(tái)可能沒有 PCIe 硬核,或者無法承擔(dān)高昂的硬件成本。 NVMe SPCle IP 正是為這樣的場景量身定制。通過結(jié)合 PCIe 軟核 IP 與 NVMe 主機(jī)控制器,讓開發(fā)人員在無硬核的情況下,也能輕松接入 NVMe SSD,突破了傳統(tǒng)存儲(chǔ)方案的硬件限制。 簡單來說,NVMe SPCle IP 的存在,讓高性能存儲(chǔ)不再是高成本設(shè)備的專屬。

ALINX NVMe SPCle IP 詳情 IP 資源消耗表 注:IP實(shí)際邏輯資源消耗受實(shí)例化中其他邏輯資源消耗影響

產(chǎn)品特性

ALINX NVMe SPCle IP 應(yīng)用交互 如圖所示,ALINX NVMe SPCIe IP 包含的 PCIe 軟核 IP,完成了 PCIe 協(xié)議的數(shù)據(jù)鏈路層和物理層的部分功能。其物理接口通過 PIPE 接口與 AMD PCIe PHY 連接,AMD PCIe PHY 包括收發(fā)器和均衡器邏輯,用于實(shí)現(xiàn)高速數(shù)據(jù)傳輸。 NVMe SPCIe IP 由 NVMe IP 和 PCIe 軟核 IP 組成,因此 NVMe SPCIe IP 在功能上與 NVMe AXI IP 相似性。 下表顯示了 NVMe SPCIe IP 和 NVMe AXI IP 的比較信息。 如圖所示,NVMe SPCIe IP 的主要優(yōu)點(diǎn)是不需要使用 PCIe 硬核 IP。因此,SSD 的最大數(shù)量不受 PCIe 硬核 IP 數(shù)量的限制,而是受收發(fā)器模塊數(shù)量和資源的限制。但是 NVMe SPCIe IP 的資源消耗較 NVMe AXI IP 高,且僅支持 4 Lane PCIe Gen3 SSD。

ALINX NVMe IP 選型 ALINX 推薦在需要大容量存儲(chǔ)和高速存儲(chǔ)的應(yīng)用場景中,優(yōu)先使用不包含 PCIe 硬核 IP 的低成本 FPGA。 當(dāng)用戶所選設(shè)備沒有足夠的 PCIe 硬核 IP 來連接所有 NVMe SSD 時(shí),可以同時(shí)使用 NVMe AXI IP 和 NVMe SPCIe IP 進(jìn)行系統(tǒng)設(shè)計(jì),如下圖所示。 當(dāng)所選 FPGA 器件已經(jīng)集成了 PCIE 硬核 IP,并且數(shù)量足夠時(shí),建議使用 NVMe AXI IP 進(jìn)行設(shè)計(jì),以減少 FPGA 資源的占用。 有關(guān) NVMe IP 的更多信息,您可以隨時(shí)聯(lián)系 ALINX 進(jìn)行咨詢 (021-67676997) 。ALINX 還可為您提供 FPGA 器件的參考設(shè)計(jì)評(píng)估服務(wù),幫助您選擇最合適的產(chǎn)品和方案。